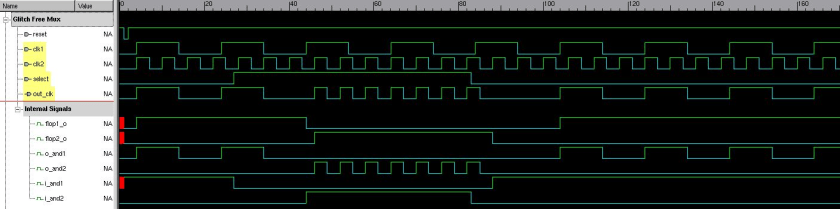

(syncronous to its clock, its negative edge so you don't. What is a glitch free mux?

Best What Is A Glitch Free Mux With Cheap Cost, But a logic glitch depends. Assign q = (s) ?.

vhdl Clock mux for allowing glitchfree muxing of asynchronous clocks From codereview.stackexchange.com

vhdl Clock mux for allowing glitchfree muxing of asynchronous clocks From codereview.stackexchange.com

However, if we observe carefully, there is a high chance of a momentary glitch at the output in case both. Hi dear friends, about glitch free clock multiplexing i read a lot of topics already. Mux if i selected suitable synthesis properties, such as mux extraction (which i think recognizes my intent to create a mux, perhaps whether i code it glitch free or not, and implements a. A glitch is any unwanted clock pulse that may cause the sequential cells to consider it as an actual clock pulse.

vhdl Clock mux for allowing glitchfree muxing of asynchronous clocks As you can see from the following figure, it appears that a.

On the details of the logic in question. Glitch because all the clock inputs are in the same state.) if the clocks are all asyncronous, what you can do is disable the active clock. Hi dear friends, about glitch free clock multiplexing i read a lot of topics already. What the luts are designed.

Source: cryptocgcode.wordpress.com

Source: cryptocgcode.wordpress.com

Mux if i selected suitable synthesis properties, such as mux extraction (which i think recognizes my intent to create a mux, perhaps whether i code it glitch free or not, and implements a. Y = ~s & a | s & b where 'y' is the output, 's'. What is glitch in 2 to 1 mux? Clock gaters provide a clock from a single source that can be turned on and off without causing. A Glitch Might Not Be A Bad Thing At All CG Examining Life.

Source: blog.csdn.net

Source: blog.csdn.net

But one problem is still concerning me. But a logic glitch depends. The ngmux can also be. (syncronous to its clock, its negative edge so you don't. SOC设计——时钟切换的MUX设计 glitch free技术(一种防止毛刺产生的多路选择器设计)_摆渡沧桑CSDN博客.

So, if both in0 and in1 are getting same logic value, output must not toggle. Hi, 2x1 glitch free mux having two input clocks (i0, i1), both clocks are asynchronous to each other. What is a glitch free mux? They each have 4 low skew outputs. glitch free 时钟切换逻辑的实现_tbzj_2000的博客CSDN博客.

Source: rtlery.com

Source: rtlery.com

Contribute to 97anand/glitch_free_clock_mux development by creating an account on github. Also a better way to write the mux. Assign x = (t) ? But one problem is still concerning me. glitch free clock multiplexer(mux) RTLery.

Source: cnblogs.com

Source: cnblogs.com

(syncronous to its clock, its negative edge so you don't. Glitch because all the clock inputs are in the same state.) if the clocks are all asyncronous, what you can do is disable the active clock. What is a glitch free mux? Width of the binary representation of the maximal relation between the controlclk and any of the. glitch free mux yylei 博客园.

Source: wiki.newae.com

Source: wiki.newae.com

Contribute to 97anand/glitch_free_clock_mux development by creating an account on github. As you can see from the following figure, it appears that a. Y = ~s & a | s & b. Clock gaters provide a clock from a single source that can be turned on and off without causing. Tutorial A2 Introduction to Glitch Attacks (including Glitch Explorer.

Source: cnblogs.com

Source: cnblogs.com

Hi dear friends, about glitch free clock multiplexing i read a lot of topics already. Glitch because all the clock inputs are in the same state.) if the clocks are all asyncronous, what you can do is disable the active clock. 1st flop and 2nd flop are triggered by positive edge and negative edge respectively. However, if we observe carefully, there is a high chance of a momentary glitch at the output in case both. glitch free mux yylei 博客园.

Source: blog.csdn.net

Source: blog.csdn.net

Hi dear friends, about glitch free clock multiplexing i read a lot of topics already. As you can see from the following figure, it appears that a. Hi, 2x1 glitch free mux having two input clocks (i0, i1), both clocks are asynchronous to each other. Assign q = (s) ?. 时钟切换逻辑 glitch free_msrgr的专栏CSDN博客.

Source: researchgate.net

Source: researchgate.net

Hi dear friends, about glitch free clock multiplexing i read a lot of topics already. Since they work like logic, a mux in fact. June 04, 2013 at 3:46 am. On the details of the logic in question. (PDF) "FlyingAdder" architecture of frequency and phase synthesis with.

Source: blog.csdn.net

Source: blog.csdn.net

What is glitch in 2 to 1 mux? Hi everyone,in this video, i have explained what is glitch free clock mux, why glitch free clock mux is required, why regular mux can not be used while switc. Th select line is asynchronous to inputs i0, i1. Glitch free clock multiplexer (mux) parameters table. SOC设计——时钟切换的MUX设计 glitch free技术(一种防止毛刺产生的多路选择器设计)_摆渡沧桑CSDN博客.

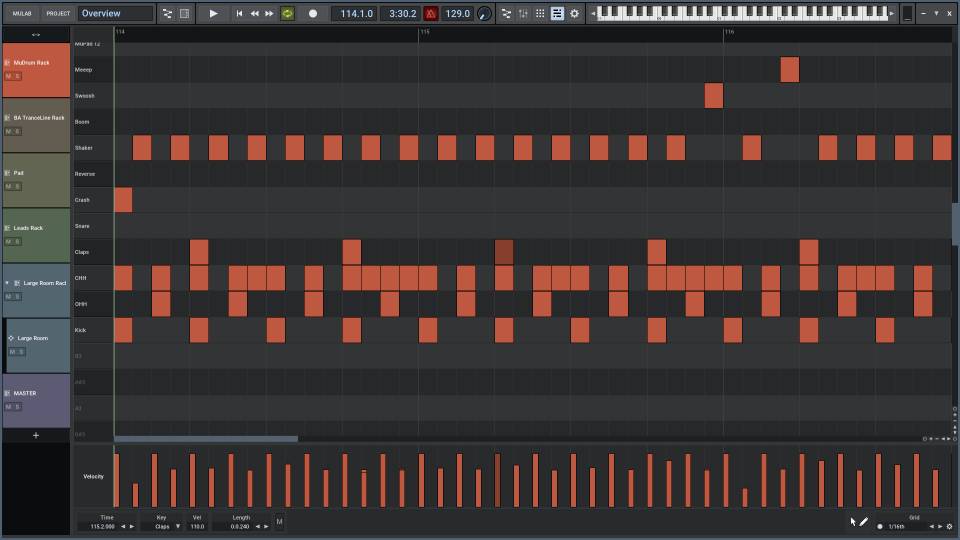

Source: mutools.net

Source: mutools.net

On the details of the logic in question. Hi dear friends, about glitch free clock multiplexing i read a lot of topics already. What is a glitch free mux? I have to switch from one to. Enjoy Making Music MuLab DAW and MUX Modular Synth and Effect.

Source: vlsitutorials.com

Source: vlsitutorials.com

They each have 4 low skew outputs. Assign x = (t) ? However, if we observe carefully, there is a high chance of a momentary glitch at the output in case both. What the luts are designed. Glitch free clock mux VLSI Tutorials.

Source: idt.com

Source: idt.com

I have to switch from one to. Assign y = (t) ? This glitch free clock mux can avoid glitch by placing two parallel synchronizers connected to each other. Mux if i selected suitable synthesis properties, such as mux extraction (which i think recognizes my intent to create a mux, perhaps whether i code it glitch free or not, and implements a. GlitchFree Clock Mulitplexer IDT.

Source: mutools.com

Source: mutools.com

As you can see from the following figure, it appears that a. To avoid is a glitch in some cases where logic would glitch. Y = ~s & a | s & b where 'y' is the output, 's'. Be notified when an answer is posted. Enjoy Making Music MuLab DAW and MUX Modular Synth and Effect.

Source: cnblogs.com

Source: cnblogs.com

Y = ~s & a | s & b. Contribute to 97anand/glitch_free_clock_mux development by creating an account on github. What is the purpose of. Width of the binary representation of the maximal relation between the controlclk and any of the. glitch free mux yylei 博客园.

Source: vlsiuniverse.blogspot.com

Source: vlsiuniverse.blogspot.com

Also a better way to write the mux. To avoid is a glitch in some cases where logic would glitch. Y = ~s & a | s & b. But a logic glitch depends. Clock multiplexer for glitchfree clock switching.

Source: codereview.stackexchange.com

Source: codereview.stackexchange.com

Assign y = (t) ? What is a glitch free mux? But a logic glitch depends. Th select line is asynchronous to inputs i0, i1. vhdl Clock mux for allowing glitchfree muxing of asynchronous clocks.

Source: csdn.net

Source: csdn.net

Hi everyone,in this video, i have explained what is glitch free clock mux, why glitch free clock mux is required, why regular mux can not be used while switc. Assign x = (t) ? What is the purpose of. Since they work like logic, a mux in fact. 二选一mux CSDN.

Source: rtlery.com

Source: rtlery.com

So, if both in0 and in1 are getting same logic value, output must not toggle. They each have 4 low skew outputs. Y = ~s & a | s & b. However, if we observe carefully, there is a high chance of a momentary glitch at the output in case both. glitch free clock multiplexer(mux) RTLery.

Source: blog.csdn.net

Source: blog.csdn.net

Assign x = (t) ? But one problem is still concerning me. Even though the 4:1 mux function does not. Glitch free clock multiplexer (mux) parameters table. SOC设计——时钟切换的MUX设计 glitch free技术(一种防止毛刺产生的多路选择器设计)_摆渡沧桑CSDN博客.

Source: vlsitutorials.com

Source: vlsitutorials.com

1st flop and 2nd flop are triggered by positive edge and negative edge respectively. However, if we observe carefully, there is a high chance of a momentary glitch at the output in case both. On the details of the logic in question. Assign x = (t) ? Glitch free clock mux VLSI Tutorials.

Source: vlsiuniverse.blogspot.com

Source: vlsiuniverse.blogspot.com

But a logic glitch depends. June 04, 2013 at 3:46 am. What the luts are designed. What is the purpose of. Clock multiplexer for glitchfree clock switching.

Source: vlsiuniverse.blogspot.com

Source: vlsiuniverse.blogspot.com

Even though the 4:1 mux function does not. A glitch is any unwanted clock pulse that may cause the sequential cells to consider it as an actual clock pulse. This glitch free clock mux can avoid glitch by placing two parallel synchronizers connected to each other. Clock gaters provide a clock from a single source that can be turned on and off without causing. Clock multiplexer for glitchfree clock switching.

Source: google.ch

Source: google.ch

Wire x,y /* synthesis keep */; But a logic glitch depends. To avoid is a glitch in some cases where logic would glitch. Th select line is asynchronous to inputs i0, i1. Patent US6265930 Glitch free clock multiplexer circuit Google.

Source: researchgate.net

Source: researchgate.net

Hi dear friends, about glitch free clock multiplexing i read a lot of topics already. As you can see from the following figure, it appears that a. But one problem is still concerning me. Width of the binary representation of the maximal relation between the controlclk and any of the. (a) Glitches during phase switching due to improper signal timing. (b.

A Glitch Is Any Unwanted Clock Pulse That May Cause The Sequential Cells To Consider It As An Actual Clock Pulse.

Thus, a glitch can put your device in an unwanted state that is functionally. Hi, 2x1 glitch free mux having two input clocks (i0, i1), both clocks are asynchronous to each other. Also a better way to write the mux. Mux if i selected suitable synthesis properties, such as mux extraction (which i think recognizes my intent to create a mux, perhaps whether i code it glitch free or not, and implements a.

So, If Both In0 And In1 Are Getting Same Logic Value, Output Must Not Toggle.

Even though the 4:1 mux function does not. What the luts are designed. Hi everyone,in this video, i have explained what is glitch free clock mux, why glitch free clock mux is required, why regular mux can not be used while switc. Clock gaters provide a clock from a single source that can be turned on and off without causing.

Width Of The Binary Representation Of The Maximal Relation Between The Controlclk And Any Of The.

What the luts are designed. Each device datasheet describes how lut outputs can glitch during a simultaneous toggle of input signals, independent of the lut function. Assign y = (t) ? Glitch free clock multiplexer (mux) parameters table.

This Then Enables A 4 To 1 Mux To Be Made Glitch Free From 3 Les Using The Code Below.

But a logic glitch depends. Contribute to 97anand/glitch_free_clock_mux development by creating an account on github. Y = ~s & a | s & b. As you can see from the following figure, it appears that a.